En la siguiente entrada vamos a realizar un ejercicio de

CPLD´s cuya finalidad es realizar el estudio de la creación de un símbolo a

partir de un módulo basado en una maquina de estados tipo Mealy.

Una máquina de estados se puede

definir, como un dispositivo digital capaz de ser atravesado por una secuencia

predeterminada de estados de una manera ordenada, de forma que el valor de su

salida, en un instante determinado, no depende de los estados lógicos de las

entradas, sino de la secuencia con que dichos estados se apliquen a las

entradas.

En un circuito secuencial existen:

‘n’ variables de entrada. -> 2n estados de entrada

‘m’ variables de memoria. -> 2m estados internos

‘p’ variables de salida. -> 2p estados de salida

A las máquinas de estados se las conoce como autómatas

finitos.

Vamos a seguir los siguientes pasos:

1.

Escribir las condiciones de transición y las acciones

de los estados, en un lenguaje de sintaxis independiente.

2. Exportar el diagrama a un lenguaje VHDL, Verilog o

ABEL

3.

Sintetizar el fichero HDL resultante para crear

un netlist o macro que podamos utilizar en nuestro esquemático.

El enunciado es el siguiente:

Se desea proyectar el gobierno de un

conmutador rotativo, que permite realizar un ciclo completo cuando el tambor haya

efectuado una vuelta completa.

El disco solidario del tambor lleva un

saliente para actuar sobre el contacto (a).

El pulsador (b) (botón de

impulsos) da comienzo al ciclo.

1) Estado inicial (reposo) a=1,

b=0, M=0.

2) (b) es accionado y después

desaccionado rápidamente (impulso) -> M=1.

3) Cuando el disco ha dado una vuelta, (a) es

accionado por el saliente y el disco se para.

Comenzaremos realizando un análisis del desarrollo

mediante el diagrama de flujo síncrono que será utilizado en el diseño gráfico principal.

La Tabla de

estados enumerará los posibles estados de la máquina, los cuales no han de

ser confundidos con los estados internos que se necesitarán para registrar todo

el proceso secuencial.

En nuestro caso será el siguiente:

Estado b a M

0 0

1 0

1 1 1 1

2 0 1 1

3 0 0 1

4 1 0

1

5 1 1 0

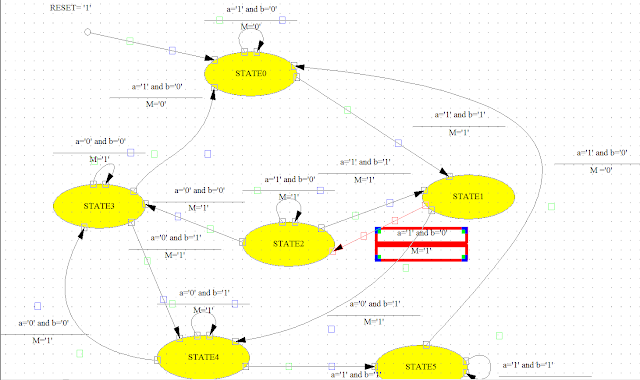

El diagrama

de flujo consiste en expresar gráficamente la secuencia del proceso, de la

máquina rotativa, con sus estados inestables, estables y valores de salida.

En sí, este diagrama es la solución

del ejercicio.

Ahora vamos a proceder a realizar el

diseño de especificación del ejercicio utilizando un lenguaje de representación

gráfico por medio de la herramienta gráfica integrada en ISE conocida como ECS

que ya hemos utilizado en anteriores ejercicios.

Realizaremos el siguiente esquema:

Comenzaremos creando un nuevo

proyecto y añadiremos una nueva fuente

esquemática.

Añadiremos además una nueva fuente de

estado de diagramas (state diagram) abriéndose la herramienta StateCAD.

Vamos a añadir los puertos de entrada

y de salida de la máquina, para lo cual entraremos en Options à

Variable.

En la ventana que se nos abre vemos

que por defecto existe la entrada de reloj.

Los demás puertos se añaden poniendo

el nombre en el campo ‘Name’, configurando el tipo, el

modo activo y si va a ser un pin o un nodo interno.

Posteriormente hacemos clic en el botón ‘Add/Modify’.

Una vez finalizado pulsamos OK y

comenzamos con el diseño del autómata.

Comenzaremos añadiendo los estados, en

este caso 6 estados que son todos los posibles.

Ahora dibujaremos las transiciones tal y como nos indica el

diagrama de flujo definido al comienzo

Añadimos un ‘RESET’ al

diseño seleccionando el botón ‘Add Reset’ en la barra de herramientas y lo situamos en el ‘ESTADO 0’.

Una máquina de estados debe tener un ‘reset’ de forma que

arranque en el estado correcto.

El ‘reset’ puede

trabajar en alto o bajo activo y ser asíncrono o síncrono (en nuestro caso es

asíncrono y trabajaen alto activo).

Damos valor a las ecuaciones de

entradas y a las salidas. Poniendo el cursor encima de las transiciones y haciendo

clic, con el botón izquierdo del ratón, se nos abrirá la siguiente ventana:

Definiremos las condiciones de

entrada--condición y los valores de salida--outputs:

Verificamos el correcto funcionamiento

del autómata creando un ‘test bench’. Hacemos clic sobre el botón

de ‘State Bench’.

Se nos abrirá una nueva ventana en la

cual podemos simular los estados modificando las variables existentes.

Comenzaremos dándole un reset al autómata,

observando que el estado que se nos pone de color amarillo es el estado 0 y la

transición del reset por la que ha pasado se pone en color verde.

Para pasar al siguiente

estado, deberemos pinchar en las entradas a modificar, en este caso tanto a como

b y pulsaremos el botón cycle para que pase un ciclo de trabajo y aparezca el

nuevo estado.

Una vez verificado el funcionamiento

generamos el código del autómata en VHDL haciendo clic en ‘Generate

HDL’.

El código VHDL se nos muestra en una

ventana donde podemos observar como la entidad está formada por las entradas a,

b, CLK, RESET y por la salida M. Esta entidad es, en sí, el componente

que posteriormente generaremos.

Cuando voy a crear el símbolo del

esquemático me da error

No hay comentarios:

Publicar un comentario