En la siguiente entrada vamos a realizar el siguiente

ejercicio de CPLD´S:

Implementar en el CPLD XC9572 un Contador

BCD con permiso de reloj y borrado asíncrono. Su salida será decodificada a

7 segmentos sobre una DISPLAY de cátodo común de 7 segmentos.

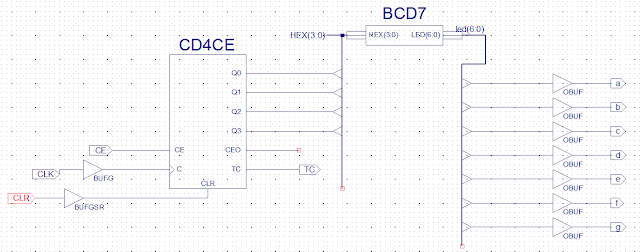

El esquema general de cómo ha de

funcionar sería el siguiente:

Antes de comenzar con el diseño, será

necesario realizar un análisis de la decodificación que será necesario

realizar, mediante el lenguaje descriptivo del hardware VDHL:

DECODIFICADOR BCD 7 sg

entity bcd7seg is

Port ( HEX : in std_logic_vector(3 downto 0);

LED : out std_logic_vector(6 downto 0));

end bcd7seg;

architecture Behavioral of bcd7seg is

begin

with HEX select

LED<= "0000110" when

"0001", --1

"1011011" when

"0010", --2

"1001111" when

"0011", --3

"1100110" when

"0100", --4

"1101101" when

"0101", --5

"1111101" when

"0110", --6

"0000111" when

"0111", --7

"1111111" when

"1000", --8

"1101111" when

"1001", --9

"1110111" when

"1010", --A

"1111100" when

"1011", --b

"0111001" when

"1100", --C

"1011110" when

"1101", --d

"1111001" when

"1110", --E

"1110001" when "1111", --F

"0111111" when others; --0

end Behavioral;

Una vez

realizado el análisis de la decodificación vamos a proceder a realizar la

especificación utilizando la herramienta gráfica de esquemas integrada en el ya

utilizado anteriormente entorno ISE llamada ECS.

Comenzaremos

al igual que en otros ejercicios creando el nuevo proyecto y añadiendo una

nueva fuente esquemática.

Los

componentes que vamos a incorporar al diseño son, un contador BCD llaado “CD4CE”,

un buffer global de reloj llamado BUFG y otro buffer global pero de set/reset

llamado BUFG y con el valor SR.

Este valor

se utilizará en los casos que necesitemos utilizar un set, un reset, un preset

o un clear en varios dispositivos. Con este valor estaremos utilizando la net

interna “global set/reset”.

Necesitamos crear

el decodificador BCD-7seg en código VHDL, que llamaremos bcd7.

Para ello

generaremos una nueva fuente del tipo VHDL module, que una vez seleccionado nos

mostrará un ayudante del sistema para configurarlo y poder generar así el

código VHDL siendo la arquitectura utilizada del tipo Behavorial.

Para

finalizar habrá que indicar los puertos de la entidad, el bus que llamaremos

HEX de 4 entradas y otro bus de 7 salidas que llamaremos LED.

El archivo

que hemos generado es una plantilla en la que se ha definido la entidad,

faltando por lo tanto la arquitectura que describa el funcionamiento de la

entidad.

Para ello,

ISE posee plantillas que definen diversos tipos de elementos, existiendo uno

que corresponde con el que vamos a utilizar llamado “7-Segment Display”.

Para acceder a él deberemos buscar en Edit Language Templates.

Una vez

localizado procederemos a copiar y pegar en nuestra arquitectura.

Como podeis

observar en el código introducido, este ha sido realizado para utilizar un

display de ánodo común, utilizando nosotros uno de katodo común por lo que será

necesario variar los datos binarios de la columna izquierda.

Una vez

realizado el cambio guardaremos todos los archivos y crearemos el esquemático

Ya creado lo

llamaremos para incluirlo en nuestro esquema principal.

No hay comentarios:

Publicar un comentario